PCI Express AXI Manager

Note

PCI Express® AXI master has been renamed to PCI Express AXI manager and the PCIe MATLAB® as AXI Master IP has been renamed to the PCIe AXI Manager IP. In the software and documentation, the terms "manager" and "subordinate" replace "master" and "slave," respectively.

When using PCI Express AXI manager, you must first include the following two intellectual property (IP) blocks in your Quartus® Qsys project.

PCIe AXI Manager IP

PCIe AXI Manager is an HDL IP provided by MathWorks®. This IP connects the PCI Express (PCIe) core to your application code. It also has a configuration port for accessing configuration registers. This block diagram shows the interface to the HDL IP.

The interface includes the following parts:

clockandresetnare the clock and reset inputs. Connect them to the AXI clock and reset.axs_sois a 32-bit subordinate interface and is used for accessing the PCIe configuration registers. Connect this interface to the Avalon Memory Mapped master interface.axm_pcieis a 128-bit AXI manager interface. Connect this interface to the TX subordinate port on the PCIe core.axm_appis a 128-bit AXI manager interface. Connect this interface to your application logic.

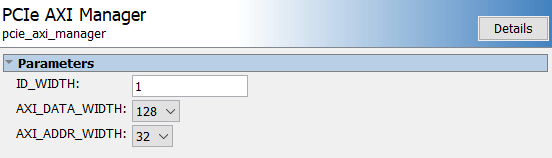

After instantiating this IP in your design, open the block parameters for configuration.

Configure these parameters:

ID_WIDTH – This parameter is the ID width in bits. Its value must match the ID width of the AXI subordinate.

AXI_DATA_WIDTH – This parameter is the data bus width. The IP supports only 128-bit data. This parameter is not identical to the data width of the

aximanagerobject or the AXI Manager Read or AXI Manager Write blocks. If the data width is set to 32 bits, and the AXI_DATA_WIDTH of your IP is set to 128 bits, HDL Verifier™ packs four 32-bit words to transfer on the 128-bit bus.AXI_ADDR_WIDTH – This parameter is the address bus width. The IP supports 32-bit address.

PCI Express Core

The Hard IP for PCI Express Core is a board-specific IP provided by Intel®. Use this IP for configuring and integrating the PCI Express port.

After instantiating the PCIe core HDL IP in your Quartus Qsys project, configure the PCIe core using these steps (this example is for an Arria® 10 board).

On the Physical Function 0 IDs tab, set the parameters as shown in this figure.

On the Avalon-MM Settings tab, set the parameters as shown in this figure.

On the System Settings tab, select a Hard IP mode with a bus width to match the AXI_DATA_WIDTH parameter previously set in the PCIe AXI Manager IP block parameters. (The IP currently supports 128-bit mode).

Connect the PCIe AXI Manager IP to the PCIe core (this example shows Arria 10 Hard IP for PCI Express).

Compile and build your FPGA project.

Insert the FPGA board into the PCI Express slot on the motherboard of the host computer.

Program the FPGA with your compiled design.

Restart the host machine.

Once the program is running on your FPGA board, you can create an AXI manager

object. For more information, see aximanager. To access the subordinate memory locations on the board,

use the readmemory and writememory functions of this object.