Common Causes for Dead Logic

Common modeling patterns that lead to dead logic in a model include:

When you perform design error detection analysis, Simulink® Design Verifier™ reports the common causes of dead logic in the Results window.

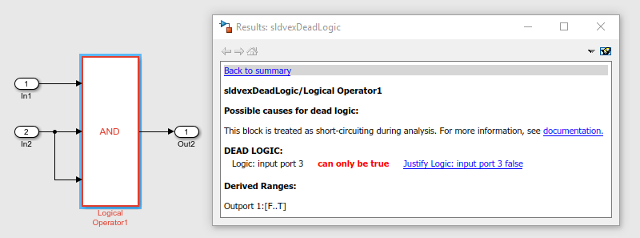

Short-Circuiting of a Logical Operator Block During Analysis

Simulink Design Verifier treats logic blocks as if they are short-circuiting when analyzing for dead logic.

For example, in this model, if In2 is false, the software

ignores the third input due to the short-circuiting. The Results window lists this

port as dead logic. See Logical Operations Short-circuiting.

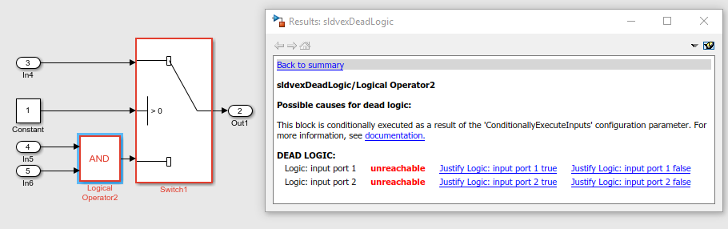

Conditional Execution of a Block

If your model consists of Switch or Multiport Switch

blocks and the Conditional input branch execution parameter is

set to On, the conditional execution can often cause

unexpected dead logic.

Consider this example model where the Conditional input branch

execution parameter is set to On. The AND

Logical Operator block is conditionally executed, which causes

the dead logic for the block. For more information, see Conditional input branch execution.

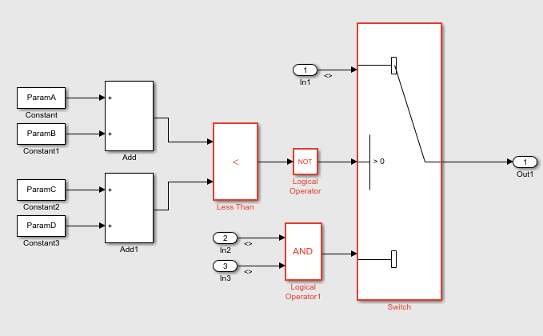

Parameter Values Treated as Constants

If your model contains parameters, Simulink Design Verifier treats the values as constants by default. This might cause dead logic in the model. In these cases, consider configuring these parameters to be tuned during analysis.

For example, consider this model, where all of the parameters are set to zero. These settings cause the dead logic for the Less Than block.

Upstream Blocks

When a particular block has dead logic, this often leads to a cascade effect that causes downstream blocks to have dead logic.

Consider the above example model. The dead logic in the Less Than block causes the dead logic in the corresponding downstream blocks. It is therefore often helpful to review the upstream dead logic before reviewing any downstream dead logic.

Library-Linked Blocks

Library blocks may be written with defensive conditions that are redundant in some of the locations where they are used. In some cases, this may cause dead logic. See Exclude and Justify Objectives for Design Error Detection.

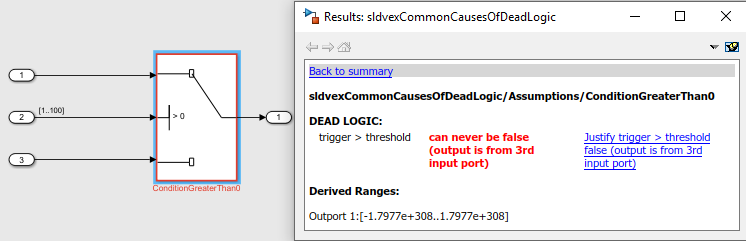

Restrictions on Signal Ranges

Root-level Inport blocks with minimum and maximum values as constraints and Test Condition blocks in the test generation may cause dead logic. For example, consider ConditionGreaterThan0 Switch block, where the second Inport block has a minimum and maximum range of 1 and 100, respectively. This causes the Switch block in this subsystem to have dead logic.