Multicore Architecture of Infineon AURIX

Microcontrollers in the Infineon AURIX TC3x family might contain up to six TriCore® processing units (TriCore 0 to TriCore 5). TriCore 0 is the principal processing unit that handles system initialization, boot processes, and critical control tasks in the AURIX microcontrollers. These processing units can run independently or collaboratively. You can assign different applications to individual processing units. To support modular and concurrent design in Simulink®, you can distribute components of a complex application across multiple processing units.

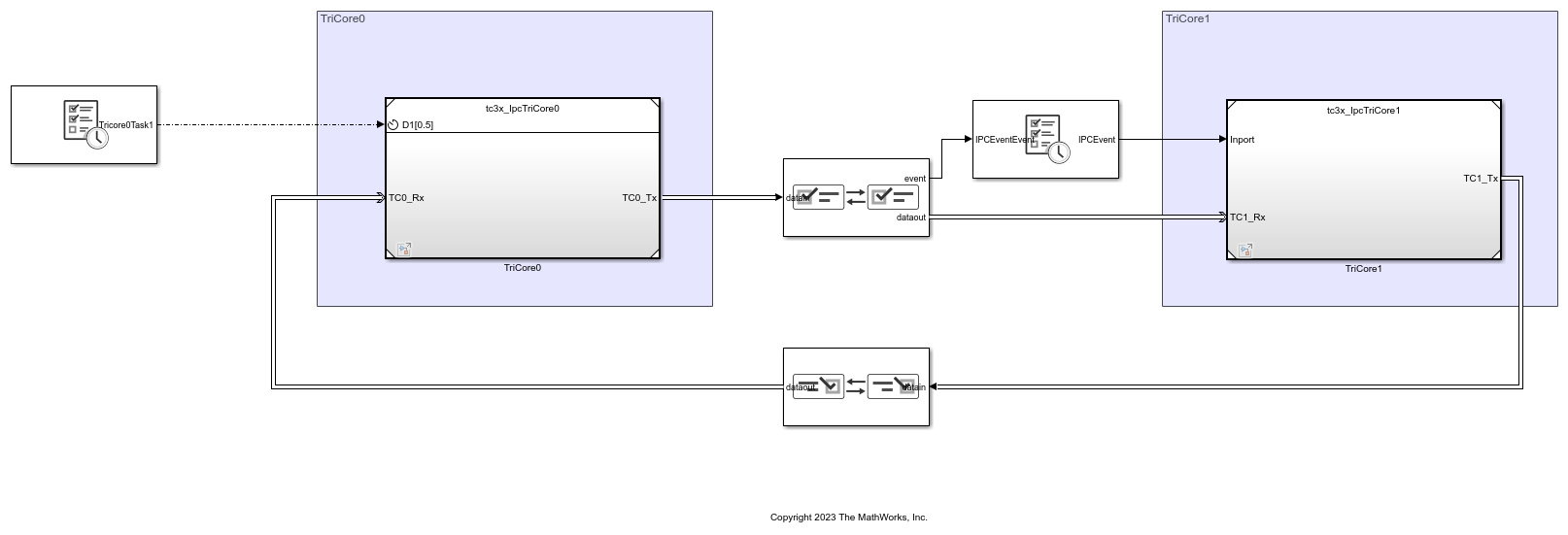

Embedded Coder® Support Package for Infineon AURIX TC3x Microcontrollers helps you to design multicore and single-core application models. The figure shows recommended modeling scenarios using different processing units of the Infineon AURIX TC4x microcontrollers.

The figure shows the recommended modeling scenarios using different processing units (PU) of the Infineon AURIX TC3x microcontrollers.

Monolithic models — A single or stand-alone Simulink model that generates one integrated application, which Simulink executes on a single processing unit.

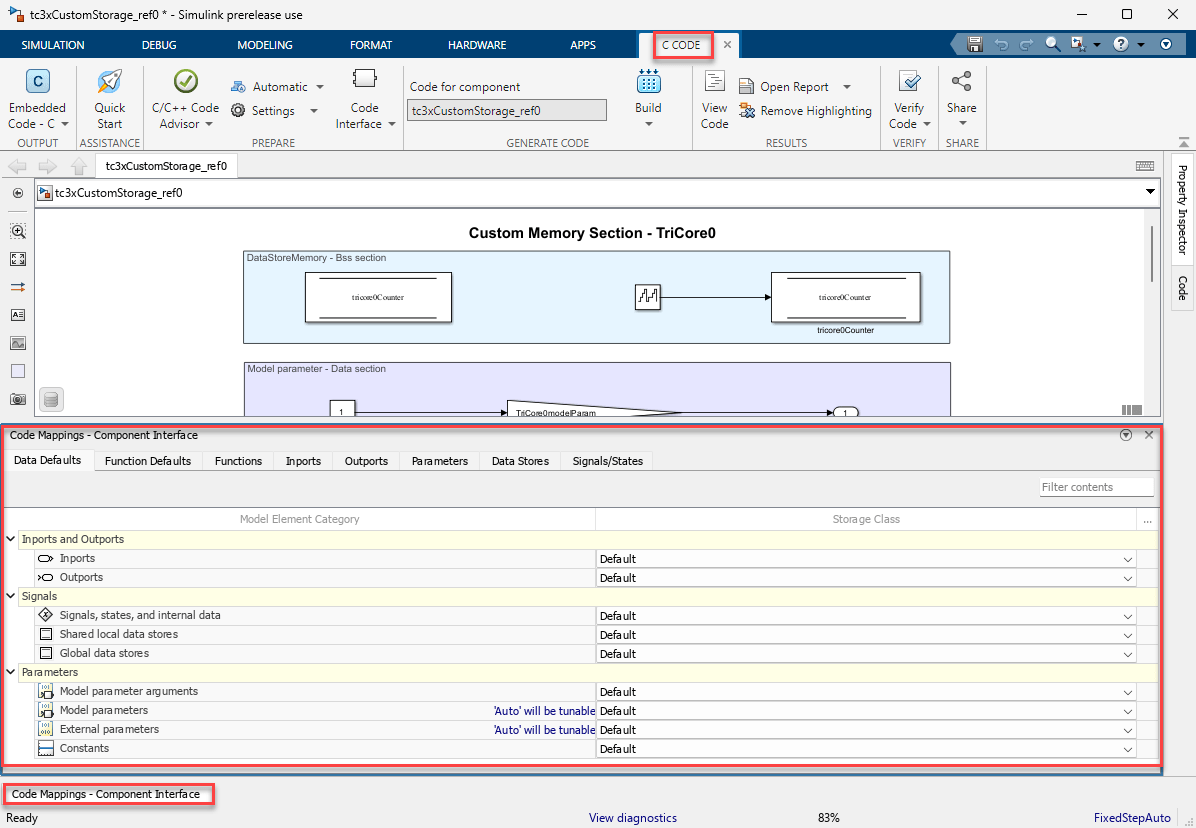

SoC-based multicore models — A unified system-on-chip (SoC) architecture that generates one or more integrated applications for the participating processing units. The SoC models consist of a top-level model and two or more unique reference models. The top-level model represents an entire embedded system with application algorithms or models running on the reference models.

Blocks

Tools

| SoC Builder | Build, load, and execute multicore application models on Infineon AURIX TC4x hardware boards (Since R2024b) |

| Hardware Mapping | Map tasks and peripherals in a model to hardware board configurations (Since R2022b) |

Topics

Modeling

- SoC-Based Multicore Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement multicore SoC models. - SoC-Based Multicore Modeling Workflow for Infineon AURIX Microcontrollers

Create SoC based multicore models.

- STEP 1: Design Time-Based Simulink Model

- STEP 2: Design Event-Based Simulink Model

- STEP 3: Configure Reference Models

- STEP 4: Design Top-Level Model

- Monolithic Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement single-core models.

Code Generation

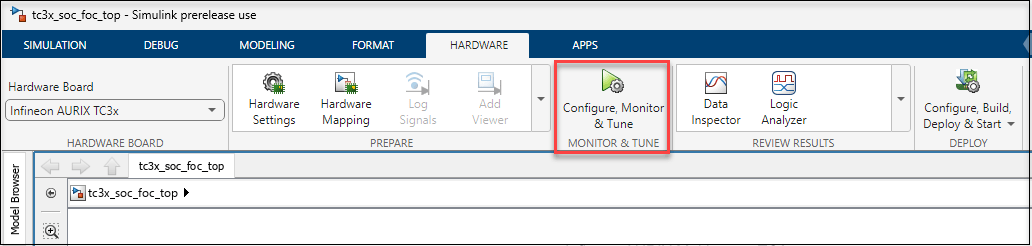

- Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool. - Generate Software Executables for Multicore Models

Generate single or multiple ELF files for all participating cores of Infineon AURIX.

Processor-in-Loop (PIL) Simulation

- Model Reference PIL Simulation

Processor-in-the-Loop (PIL) simulation techniques for Infineon AURIX hardware boards.